volatile关键字,从JMM到CPU,如何做到机械同感?

以intel为例。

回答:

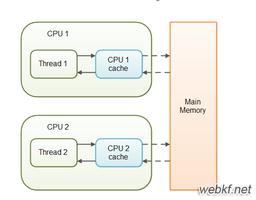

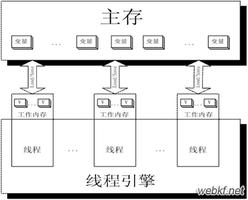

在CPU层面,volatile关键字会生成一个汇编指令,这个就相当于实现了一种内存屏障,保障该变量值在多线程下的的可见性。

具体的操作是,当线程操作volatile变量时,会写入一个屏障;

屏障的类型有LoadLoad、LoadStore、StoreLoad、StoreStore。

Load表示读,Store表示写。两两组合

在假设线程A,B按序操作volatile变量,LoadLoad屏障的意思就是:在线程B在读取操作数据前,保证线程A读取操作完毕。StoreLoad屏障的意思就是:在线程B在读取操作数据前,保证线程A写入操作完毕并对所有线程可见。

至于Intel CPU如何实现机械同感,这个问题比较复杂,内容包含了CPU架构、指令集、协议等多方面了。目前没有太过深入的了解。

不过通过不知名老哥的Java并发杂谈(一):volatile的底层原理,从字节码到CPU文章的了解,主要采用了MESI缓存一致性协议来保证缓存数据的一致性,同时也会使用锁定总线和缓存锁定等机制来实现同步的

以上是 volatile关键字,从JMM到CPU,如何做到机械同感? 的全部内容, 来源链接: utcz.com/p/945069.html