E7500 SDRAM规格发布:几安满足机速

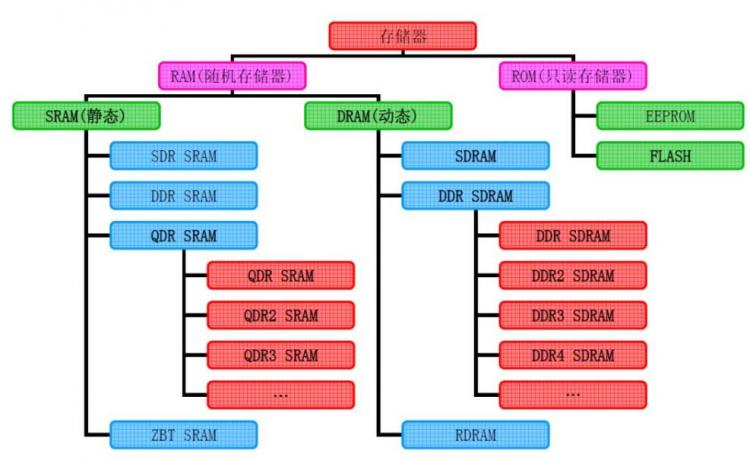

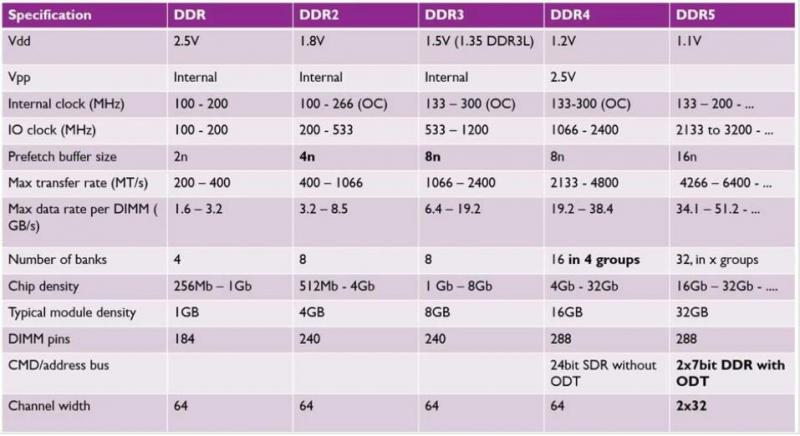

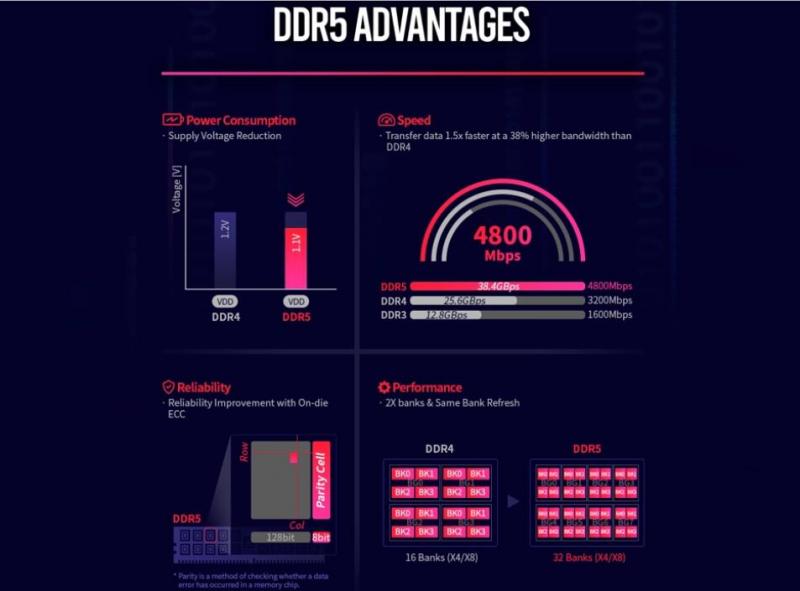

半导体工程组织JEDEC为动态随机存取存储器(DRAM)设定了标准,该组织上周发布了最终的JESD79-5DDR5规范。新型存储器是其每引脚数据传输速度的两倍,其存储设备的容量增加了四倍,降低了工作电压,并引入了多种方法来提高瘦节点上DRAM的可靠性-并降低功耗。JEDEC说,DDR5 SDRAM将从明年开始用于即将推出的客户端PC和服务器。

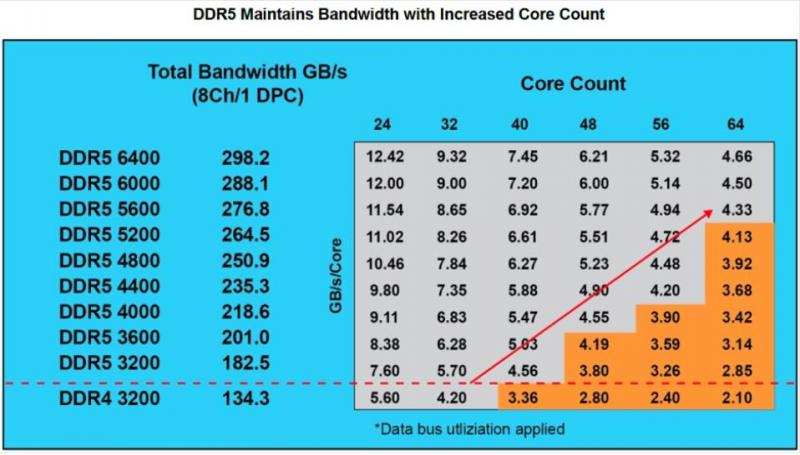

SDRAM的发展通常遵循与CPU发展相同的方向。如今微处理器致力于提高内核数,提高每个内核的性能以及提高电源效率,这对系统内存提出了要求。先进的内核需要足够的内存带宽,而此类内核的负载则需要高DRAM容量(和高带宽),但是在内存控制器的功能,信号完整性以及功耗方面存在局限性。为此,DDR5通过同时向多个方向发展DRAM来满足客户和服务器系统的需求。

JEDEC的JC-42内存委员会主席说:“通过在其设计中实现几种新的性能,可靠性和省电模式,DDR5准备支持和启用下一代技术。

DDR5带来了无数的发展,并且由于新标准提供了所有可扩展性和改进的选择,由于技术转换通常较慢,因此新型内存的寿命可能比其前代产品长-这是一件好事适用于CPU和SoC设计人员。正式出版物表明开发已完成,所有参数均已设置,并且不添加任何新功能。

高性能计算所需要的内存必须能够跟上当今处理器不断增长的需求,随着DDR5标准的发布,AMD可以更好地设计其产品,以满足我们的客户和最终用户的未来需求。

容量提高

尽管如今客户端和服务器机器在组件方面有很大不同,但它们有一个共同点:它们渴望获得高密度DRAM。随着服务器CPU内部内核数量的增加,现代服务器对内存容量的需求不断增长,但是,如果不使用带有缓冲区的复杂内存子系统(例如,LRDIMM或其他缓冲解决方案),今天在物理上不可能在每个内存通道上安装两个以上的模块。PC的DRAM需求增长速度要慢得多,但是由于我们希望使用更时尚的笔记本电脑,因此PC制造商使用了更昂贵的LPDDR内存。巧合的是服务器和客户端的答案都是相同的:更高容量的通用DRAM设备。

CadenceIP集团表示DDR5主要是关于密度,使其特别适合企业,云和大数据应用程序。

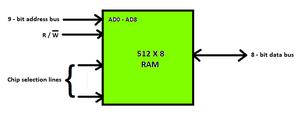

DDR5将以8GB和16GBDRAM开始,而今天的DDR4正是如此。但是该标准允许制造商设计具有24GB,32GB或64GB容量的设备。DDR4将每个设备的最大容量从8GB增加到16GB,而DDR5则从16GB一直增加到64GB,是原来的四倍。此外,DDR5最多可堆叠16个存储设备(DDR4则为四个)。但是有一个局限性:该标准最多可堆叠16个DRAM,这些DRAM具有16GB,24GB或32GB的容量,但最多只能堆叠8个64GB的设备。

高位地址位是芯片ID还是高位地址位都有限制,因此对于64GB的设备,我们只能支持8-Hi堆栈。8-Hi64GB以及16-Hi32GBDRAM堆栈将使制造商能够在未来数年内生产2TB服务器级模块,因此支持8个内存通道和每个通道两个模块的服务器CPU可以配备64个TB5DDR5内存(今天为4TB)。

由于DDR5实际上在命令/地址中嵌入了等级信息(芯片ID),而不是像前几代那样使用单独的信号,因此DDR5实现实际上可以支持多达32个等级(设备)的内存,因为我们可以拥有16个高3D堆栈记忆,模块本质上是1或2级,然后模块上的每个DRAM位置都可以支持16-Hi堆栈,因此网络为32。

由于制造上的挑战,紧凑包装的16-HiDDR5堆栈肯定不会在第一批DDR5芯片中提供。由于必要的额外制造工作,业界不太可能在DDR5中首次推出16-Hi堆栈。实际上,8-Hi堆栈可能会来得很晚。2-Hi和4-Hi堆栈的内存非常普遍,因此从一开始就意味着2、4和8级模块将非常普遍。我们不再真正将它们称为等级,而是指我们正在使用3D堆栈存储器的事实。

为了将每个设备的容量增加到64Gb,DDR5开发人员必须增加存储库的数量来解决这个问题。为此DDR5将存储库组的数量从16个增加到32个,而每个存储库组的存储库数量保持不变(四个存储库),这允许在任何给定时间打开更多页面以提高页面点击率,仅可减轻更高的容量,但实际上可以提高系统性能,这是美光公司使用其16Gb DDR5器件测得的。

以上是 E7500 SDRAM规格发布:几安满足机速 的全部内容, 来源链接: utcz.com/a/55248.html