ISE写的.vhd用ISim仿真时输入全是‘U’

4位的移位寄存器,编写的代码如下

entity shift is

port(

a,clk,rst:in std_logic;

b:out std_logic

);

end shift;

architecture Behavioral of shift is

signal temp1,temp2,temp3:std_logic;

begin

process

begin

if (rst='1') then

temp1<='0';

temp2<='0';

temp3<='0';

b<='0';

elsif (rising_edge(clk)) then

temp1<=a;

temp2<=temp1;

temp3<=temp2;

b<=temp3;

end if;

end process;

end Behavioral;

编写的TestBench如下

ENTITY shift_tb IS

END shift_tb;

ARCHITECTURE behavior OF shift_tb IS

COMPONENT shift

PORT(

a : IN std_logic;

clk : IN std_logic;

rst:IN std_logic;

b : OUT std_logic

);

END COMPONENT;

--Inputs

signal a : std_logic := '0';

signal clk : std_logic := '0';

signal rst : std_logic := '0';

--Outputs

signal b : std_logic;

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

uut: shift PORT MAP (

a => a,

clk => clk,

rst=>rst,

b => b

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

a<='0';

rst<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

rst<='1';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

rst<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

a<='0';

wait for clk_period7;

a<='1';

wait for clk_period;

end process;

END;

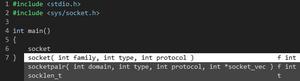

检查了很多遍觉得没有问题,而且代码可以综合并查看RTL图

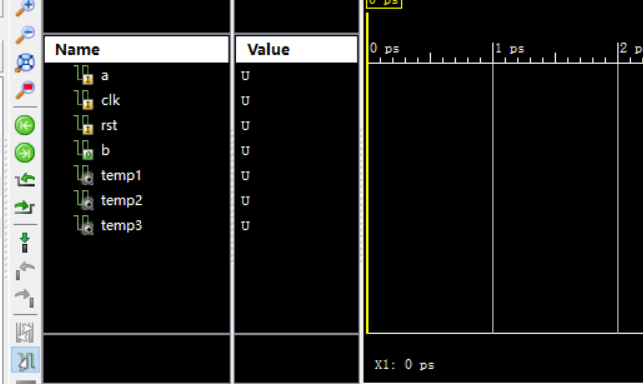

仿真界面如下

不知道是代码的问题还是仿真设置的问题,VHDL小白求帮助

回答

这是一个有点愚蠢的问题,仿真的时候应该是点击编写代码的.vhd进行仿真,我居然是点的testbench仿真的,所以出现了这样的情况。并且在源代码中process中应当加入a,clk,rst三个敏感信号。

以上是 ISE写的.vhd用ISim仿真时输入全是‘U’ 的全部内容, 来源链接: utcz.com/a/37618.html