【硬件开发技术】PCB串扰是怎么产生的,如何通过电路板走线设计消除串扰?

在课堂中,能在第一时间完整而连续地回答出相应的内容,是因为老师采用点名的方式,排除了几个人同时争抢回答而造成的干扰。

PCB上存在类似的情况,其中不同导线上的多个信号可能相互干扰。当信号传输到平行导线时产生相应的电磁能时,就被称为耦合。导体之间的耦合可以是好的也可以是坏的,可以表示为0和1(或0%和100%)之间的比率。例如,可以使用捆绑导体或双绞线电缆来实现支持良好信号传输的近乎完美的耦合比。不良耦合或串扰通常是指由于另一导体对相邻导体的信号产生扭曲或降低信号质量这类不良信号干扰。

让我们来看看串扰的原因,然后看看Altium Designer如何帮助您最大限度地减少串扰对电路板的影响。

什么原因导致串扰?

串扰是PCB设计人员必须应对的信号完整性问题之一。通常,当两个不同的信号传播路径彼此太靠近并且其各自的EM电磁场延伸超出分隔导体的空间时,发生串扰。串扰可能是数据进行高速传输中最重要的一个影响因素了。

它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。所以串扰对于综合布线来说,无疑是个最厉害的天敌。由于这种干扰是不希望的,因此可将其归类为噪声并且会导致信号失真或降低信号纯度。

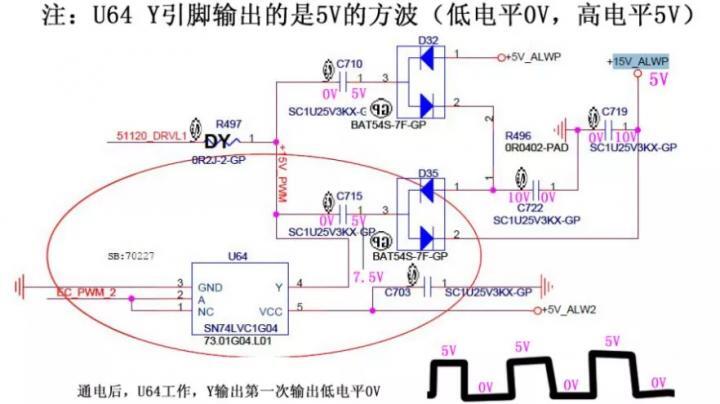

1)元件问题

随着电子产品变得越来越小,它们所包含的PCB也必须更小。然而,这些尺寸减小通常与对更大功能的需求相匹配。为了实现这些可能看起来彼此矛盾的目标,元件封装变得更小但具有更大量的网络连接或引脚数。显然,这会导致引脚间的间距变得更紧,从而促使电容耦合。引脚之间的耦合可能发生在沿着电路板表面从元件延伸的连接或从元件下方延伸,以便信号流过通孔。

2)布线问题

随着布线在电路板上占据更多空间,可能会出现更多可能发生串扰的区域。这包括在焊盘或布线路径的起点和终点,以及同一层以及层与层之间的相邻路径。焊盘上的串扰类似于元件引脚之间的串扰。在沿着导线路径上,干扰通常是由于相似长度的信号路径在相同角度处的分离不充分或具有锐角弯曲的单根导线。当叠层中的信号层未被电介质充分隔离时,也可能在不同层上的布线之间发生串扰。

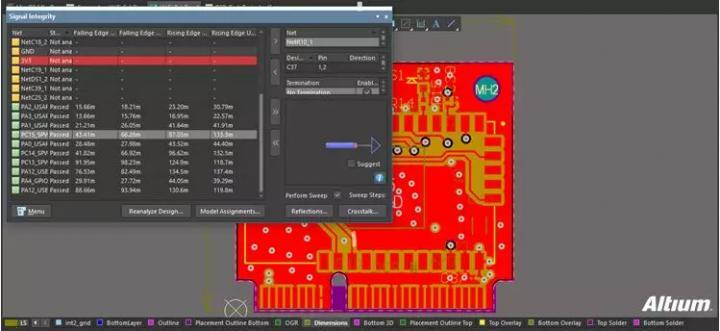

Altium Designer 中的串扰消除技术

看起来串扰对于PCB设计的良好信号完整性来说是一个不可逾越的障碍,特别是对于小而密集的复杂电路板。当然,这是一个重大的设计挑战,但有一些技术可以用来减少串扰对电路工作的影响。为了充分利用这些技术,我们首先需要能够分析我们的电路板信号,以确定是否需要消除串扰。Altium Designer提供了执行信号完整性分析的工具,如下图所示。

信号完整性分析案例

Altium中的信号完整性分析包括检查信号上升时间,下降时间,提供终端方案和进行串扰分析的能力。您还可以定义模型并设置规则和约束以及信号完整性分析相关的其它设置。一旦确认了串扰问题,就可以根据需要修改相同层或相邻层的布线路径,如下所述。

1)确保布线之间有足够的距离

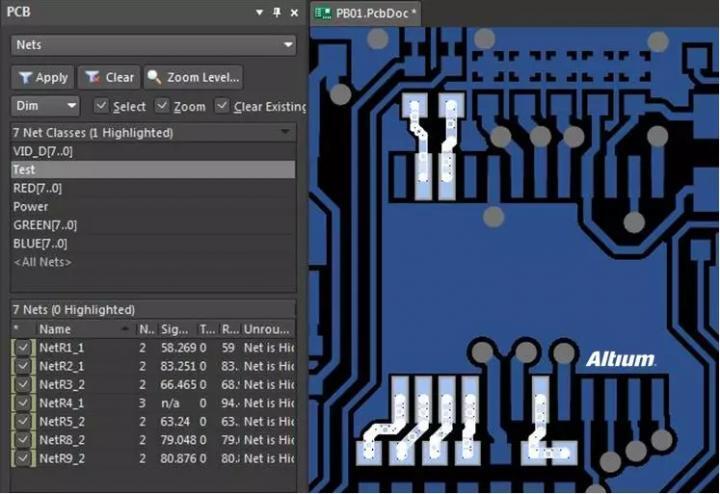

在大多数情况下,串扰的原因是有耦合关系的导体之间的间距不足。因此,减少串扰的最佳解决方案或技术是增加两个不同网络布线之间的间距。在Altium Designer中,通过使用高亮显示可以非常轻松地完成此操作,这可以让您一次移动单个元素和路径或类。在更改布线时,请务必遵循良好的PCB布局布线技巧。

使用网络类来设置布线间距

2)最小化并行走线的长度

有时,比如对于差分对,需要很好地匹配信号路径。在这些情况下,确保两个信号的铜重量,走线宽度和长度相同是重要设计目标。相反,当并行走线用于不同信号时,其重要设计目标则是最小化它们的相互作用或耦合。如果不能选择足够的间距,则可以将其中一条走线拉长,使得两条走线的并行长度尽量缩短;或者使一条走线垂直于另一条走线以减少串扰。

3)使用地平面隔离信号层

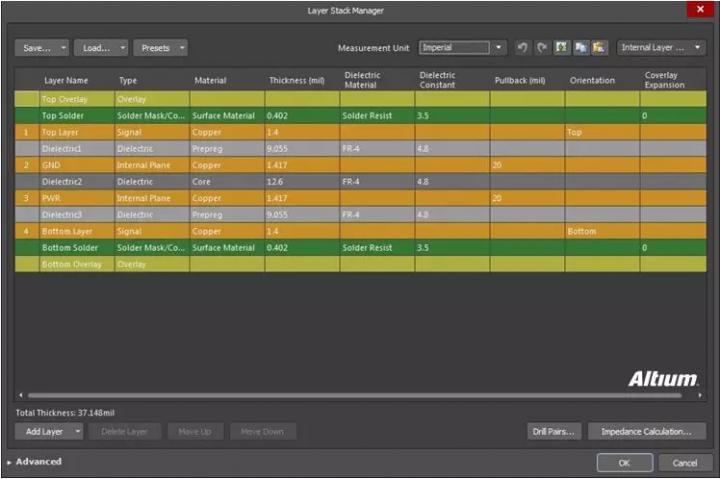

虽然相对于在同一层上产生的串扰来说,叠层之间的串扰并不常见,但确实会发生PCB叠层中相邻层之间的干扰。这种耦合的主要原因是由于层之间的绝缘不足而导致信号没有充分隔离。相邻层之间的绝缘部分是在其上蚀刻铜层的介电材料。在Altium Designer中,使用“层堆栈管理器”对话框设计堆栈是一项简单的任务。如下图所示,您可以在其中选择材料类型,设置板厚度并定义介电常数。

使用层堆栈管理器定义PCB堆栈

作为使用不同材料进行叠层的替代方案,可以在信号层之间插入接地平面。这有助于提高隔离度,有助于为您的设计提供更短的接地路径。

串扰是一种信号完整性问题,几乎可以在两个导体彼此靠近的任何位置影响PCB功能。最好的串扰消除技术是插入空间或障碍以减少耦合的技术。在应用任何这些之前,必须首先识别串扰。Altium Designer提供了一个多功能信号分析工具,可用于诊断电路板的信号并确定要应用的最佳消除技术。

原文来自:电子发烧友网

以上是 【硬件开发技术】PCB串扰是怎么产生的,如何通过电路板走线设计消除串扰? 的全部内容, 来源链接: utcz.com/a/126771.html