计算机原理与接口技术第三章8086微处理器

3.1 Intel 8086微处理器

Intel 8086微处理器是由美国Intel公司1978年推出的高性能的16位微处理器,第三代微处理器的典型嗲表,它有20根地址线,直接寻址能力达到1MB,具有16根数据总线,内部总线和ALU均为16位,可进行8位和16位操作。

3.2 8086的存储组织

寻址空间

计算机的寻址空间是由CPU地址总线的位数决定的。当存储器按字节编址时,若地址总线为n位,cpu寻址范围是2`n字节。

8086存储器的组织及寻址

8086地址总线为20位,寻址能力为1MB,每个字节用唯一的一个地址码标识。地址的范围是0-2`20-1,用十进制表示为01048575。但习惯上使用十六进制表示,即00000HFFFFFH表示。这种每个字节对应一个地址的方式成为“按字节编址”。

字节数据(BYTE)

字数据(WORD)

每个字节数据存放在两个连续的字节单元中。其中高8位存放在高地址字节,低8位存放在低地址字节,并规定将低字节的地址作为这个字的地址。

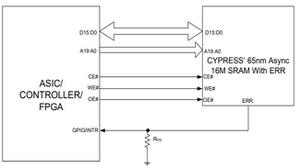

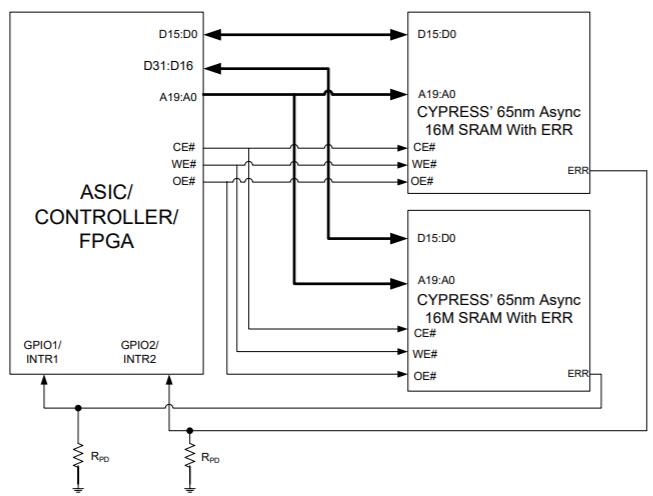

数据类型 BHE‘ A0 操作 用到的数据引脚

规则字

0

0

从偶地址开始读/写一个字

D15-D0

字节

0

1

从奇地址开始读/写一个字

D15-D8

字节

0

0

从偶地址开始读/写一个字

D7-D0

非规则字

0

1

从奇地址开始读/写一个字(非规则字),第一总线周期高八位数据有效,

D15-D8

非规则字

1

0

第二总线周期低8位数据有效

D7-D0

1

1

无效

- 存储器分段结构和物理地址形成

1.存储器的分段结构

- 8086的地址寄存器都是16位,用户不能直接使用20位的物理地址,编程时需使用逻辑地址寻址存储单元。

逻辑地址形式:段的起始地址 : 段内的偏移地址

段号 : 段内号

段:代码段(CS )、数据段(DS)、堆栈段(SS)、附加数据段(ES)

存储空间分多个逻辑段

- 1MB 最多可以分为16个段.

- 实际上,两个不同的逻辑段可以有重叠.

2.物理地址的形成

每个存储单元都有唯一物理地址,20位二进制,该地址在指令执行是有地址加法器形成,并进行硬件寻址。

地址加法器做法:段地址左移4位,加上偏移地址就得到20位物理地址。

- 一个存储单元可以拥有多个逻辑地址,但只可能拥有一个唯一的物理地址

- 例如:物理地址:00200H

- 逻辑地址:0000H : 0200H

- 逻辑地址:0020H : 0000H

3.3 8086CPU内部结构

总线接口部件BIU

- 总线接口单元BIU,负责控制存储器读写。

执行部件EU

- 执行单元EU从指令队列中取出指令并执行。

特点

- 取指和执行指令分开进行,提高了速度。

注意(位数要相等)

- mov ax,b1 错误

- mov ax,si 正确

- mov al,si Error

标志寄存器:可以存放两种状态,存放一位。

地址加法器:包含把地址左移四位的功能。

本文来自云海天,作者:涂勇军,转载请注明原文链接:https://www.cnblogs.com/tuyongjun/p/16180372.html

以上是 计算机原理与接口技术第三章8086微处理器 的全部内容, 来源链接: utcz.com/z/520384.html