Everspin串口串行mram演示软件分析

Everspin在磁存储器设计,制造和交付给相关应用方面的知识和经验在半导体行业中是独一无二的。在平面内和垂直磁隧道结(MTJ)STT-MRAM位单元的开发方面处于市场领先地位。包括40nm,28nm及更高工艺在内的先进技术节点上进行了全包交钥匙的300mm大批量平面内和垂直MTJ ST-MRAM生产。生产基于180nm,130nm和90nm工艺技术节点的MRAM产品。下面要介绍关于everspin公司MRAM演示软件分析

everspin公司MRAM演示软件分析

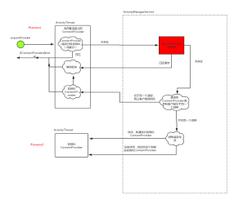

MRAM低级驱动程序通过操作系统和调度程序集成到动力总成应用程序中。读写周期由系统时钟(300MHz)测量。图1&2显示了针对动力总成应用的具有不同非易失性存储器接口的每个分区的读/写时间。这些表显示大多数读/写周期小于2ms。毫不奇怪,该表确认35ns并行接口以比40MHz串口串行mram更快的速率传输数据。

Figure 1 SPI MRAM; CLK 40MHz

使用SPI MRAM时,由于微控制器的硬件延迟(缓冲区接收/发送,设置/清除标志,读/写存储器)以及MRAM和微控制器总线之间的同步,因此读周期要比写周期花费更长的时间,与并行MRAM类似,写入周期比读取周期要花费更长的时间。1&2中显示的值包括硬件收发器,硬件延迟(收发器缓冲区,读/写存储器),LLD软件延迟以及MRAM与动力总成微控制器之间的同步。

Figure 2 EBI MRAM; CLK 66.666MHz

我们用EBI和SPI接口设备验证了不同的动力总成工作模式。 在整个地址空间范围内读写各种类型的数据。通常,MRAM的操作和时序类似于32位微控制器的规范和时序。 而且,与DLFASH相比,当今的非易失性存储器可以接受MRAM设备的性能和吞吐量。

以上是 Everspin串口串行mram演示软件分析 的全部内容, 来源链接: utcz.com/z/512887.html