什么是优先编码器?

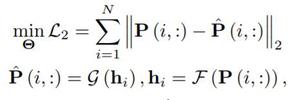

优先级编码器是执行优先级功能的电路。优先级编码器的逻辑是两个或更多输入同时出现,具有最大优先级的输入将优先。表中给出了四输入优先级编码器的真值表。表中的 X 表示无关条件。输入I 0具有最高优先级,因此当此输入为 1 时,与其他输入的值无关,输出创建输出 xy=00。

I 1具有下一个优先级。如果 I 1 =1支持I 0 =0,则输出为01 ,而不管其他两个较低优先级输入的值如何。I 2的输出仅在更高优先级的输入为 0 时才生成,等等。中断状态 IST 仅在一个或多个输入等于 1 时设置。

真值表的优先编码器

| 输入 | 输出 | 布尔函数 | |||||

|---|---|---|---|---|---|---|---|

| I0 | 我1 | I2 | 我3 | X | 是 | IST | |

| 1 | X | x | X | 0 | 0 | 1 | |

| 0 | 1 | x | X | 0 | 1 | 1 | x=I' 0 ,I' 1 |

| 0 | 0 | 1 | X | 1 | 0 | 1 | y=I' 0 ,I 1 +I' 0 ,I' 2 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | (IST)=I 0 +I 1 +I 2 +I 3 |

| 0 | 0 | 0 | 0 | x | X | 0 | |

如果所有输入都为 0,则 IST 被清除为 0,并且编码器的其他输出不被使用,因此它们被表示为无关状态。这是因为当 IST=0 时,向量地址不与 CPU 共享。表中的布尔函数决定了编码器的内部逻辑。一般来说,一台计算机会有四个以上的中断源。例如,具有八个输入的优先级编码器将创建一个三位输出。

优先级编码器的输出可以构成每个中断源的向量地址的一部分。向量地址的其他位可以创建任何值。例如,向量地址可以通过将六个零连接到编码器的 x 和 y 输出来形成。通过这个选择,四个 I/O 设备的中断向量被创建为二进制数 0、1、2 和 3。

并行优先中断

并行优先级中断技术使用一个寄存器,其位由来自每个设备的中断信号独立设置。根据寄存器中位的位置创建优先级。

除了中断寄存器之外,该电路还可以包含一个屏蔽寄存器,其目的是控制每个中断请求的状态。屏蔽寄存器可被编程为在服务高优先级设备时禁用低优先级中断。它还支持一种工具,使高优先级设备能够在为低优先级设备提供服务时中断 CPU。

以上是 什么是优先编码器? 的全部内容, 来源链接: utcz.com/z/358232.html