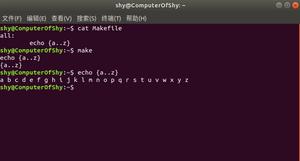

如何在makefile中编写通用命令?

这是我目前的版本是什么样子:如何在makefile中编写通用命令?

CC = gcc CFLAGS = `sdl-config --cflags`

LIBS = `sdl-config --libs` -lSDL_ttf

program: uprising

uprising: main.o init.o display.o move.o global.o control.o battle.o

$(CC) main.o init.o display.o move.o global.o control.o battle.o -o uprising $(CFLAGS) $(LIBS)

global.o: global.c

$(CC) -c global.c -o global.o $(CFLAGS)

battle.o: battle.c

$(CC) -c battle.c -o battle.o $(CFLAGS)

main.o: main.c

$(CC) -c main.c -o main.o $(CFLAGS)

init.o: init.c

$(CC) -c init.c -o init.o $(CFLAGS)

display.o: display.c

$(CC) -c display.c -o display.o $(CFLAGS)

move.o: move.c

$(CC) -c move.c -o move.o $(CFLAGS)

control.o: control.c

$(CC) -c control.c -o control.o $(CFLAGS)

clean:

rm -f *~ *# uprising init.o main.o display.o move.o global.o control.o

你看,每个模块都被以同样的方式进行编译。在向项目添加新模块时,我已经厌倦了编辑此生成文件。有没有什么办法只输入一次模块的名字(就好像它是一个参数),让makefile以同样的方式构建每个模块?

回答:

如果更改LIBS到LDLIBS,你可以在短短这个写入整个生成文件:

CC = gcc CFLAGS = `sdl-config --cflags`

LDLIBS = `sdl-config --libs` -lSDL_ttf

program: uprising

uprising: main.o init.o display.o move.o global.o control.o battle.o

$(CC) $^ -o [email protected] $(CFLAGS) $(LDLIBS)

clean:

rm -f *~ *# uprising *.o

以上是 如何在makefile中编写通用命令? 的全部内容, 来源链接: utcz.com/qa/267083.html