AMD全新Zen4内核,性能提升近半

Zen4已经是AMD Zen系列架构发布以来的第4代,虽然这款架构的革新和性能提升幅度都不是最大的,但是在Zen3基上的一步飞跃,并在新工艺的加成下巨幅提高了频率,该款最高加速的频率不仅仅首次突破了5GHz,而且还超越性地达来到了5.7GHz!

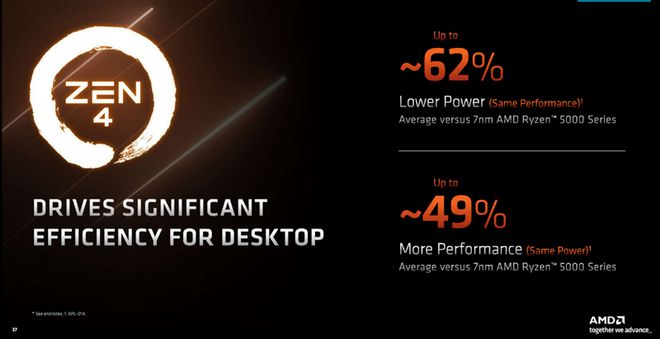

按照AMD的官方数据,Zen4相比于Zen3,同等性能下功耗可降低至多62%,同等功耗下性能可提升至多49%!

今天,我们就来深入了解一下Zen4架构、平台的革新之处,看看如此巨大的提升是从而来的。

对比四代架构,初代Zen的变革、提升幅度最猛,Zen2是一次优化升级,尤其chiplet设计奠定未来基础,Zen3则是再一次革命性的大变,19% IPC提升也非常感人,Zen4再来个小步快跑就非常符合情理和逻辑了。

按照AMD的说法,Zen4架构的设计目标有三个方面:

一是性能,IPC(每时钟周期指令数或同频性能)和频率提升幅度都要达到两位数(超过10%);

二是延迟,通过增大二级缓存、改进缓存有效性,大幅降低平均延迟;

三是能效,在整个TDP(热设计功耗)范围内,显著降低动态功耗。

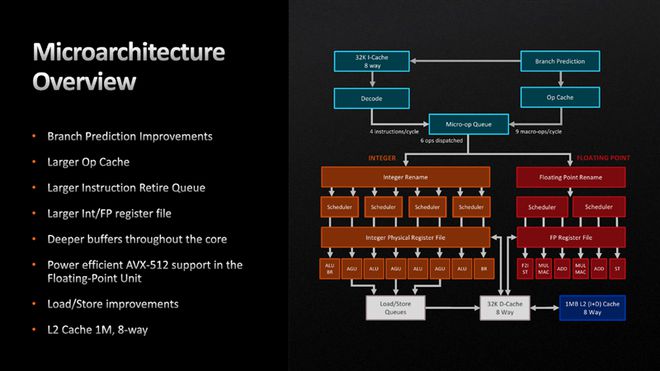

为了达成以上目标,Zen4对整个微架构体系进行了升级优化,包括前端、执行引擎、载入/存储单元、缓存、指令集等等,后边我们会一一讲到。

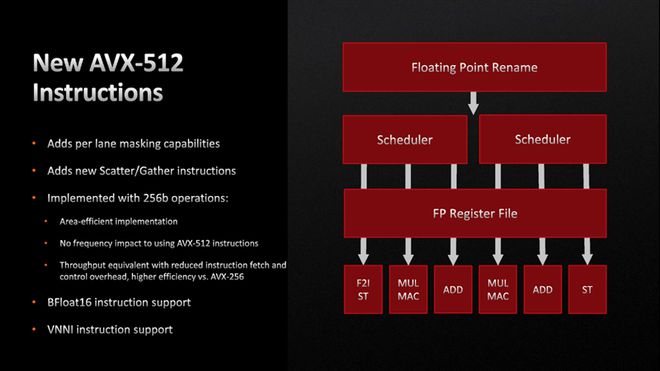

整体而言,Zen4架构的核心升级点包括:改进分支预测、增大OP指令作缓存、增大指令退役队列、增大整数/浮点寄存器文件、加深核心缓冲吞吐、浮点单元支持AVX-512指令、改进载入/存储单元、增大二级缓存。

前端部分变化较大,这里包括指令缓存、分支预测、解码器、指令缓存、微指令队列等模块。

Zen4架构重点改进了分支预测部分,包括每时钟周期预测两个跳转分支、一级缓存BTB(分支目标缓冲)增大50%达到1.5K条目、二级缓存BTB扩容从6.5K略增至7K。

另外,指令缓存(Op Cache)增大了约68%达到6.75K条目,每时钟周期可以完成多达9个宏指令(增加1个)。

不变的则是解码器每时钟周期发出4条指令、微指令队列每时钟周期分派6个整数+浮点指令。

以上是 AMD全新Zen4内核,性能提升近半 的全部内容, 来源链接: utcz.com/dzbk/762779.html