非易失性MRAM完成端口

高密度MRAM具有非常低的功率,高的读取速度,非常高的数据保留能力和耐久性,适用于广泛的应用。单元面积仅为0.0456平方微米,读取速度为10ns,读取功率为0.8mA/MHz/b,在低功耗待机模式(LPSB)下,其在25C时的泄漏电流小于55mA,相当于每比特的漏电流仅为1.7E-12A。对于32Mb数据,它具有100K个循环的耐久性,而对于1Mb的数据可以>1M个循环。它在260°C的IR回流下具有90秒的数据保留能力,在150°C的条件下可保存数据10年以上。

MRAM读取操作

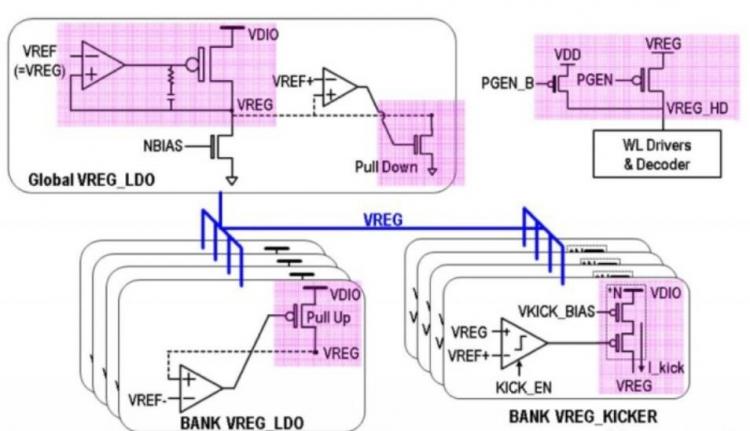

为了从LPSM快速,低能耗唤醒以实现高速读取访问,它采用了细粒度的电源门控电路(每128行一个),分两步进行唤醒(如图1所示)。电源开关由两个开关组成,一个开关用于芯片电源VDD,另一个开关用于从低压差(LDO,LowDrop-Out)稳压器提供VREG的稳定电压。首先打开VDD开关以对WL驱动器的电源线进行预充电,然后打开VREG开关以将电平提升至目标电平,从而实现<100ns的快速唤醒,同时将来自VREGLDO的瞬态电流降至最低。

MRAM写入操作

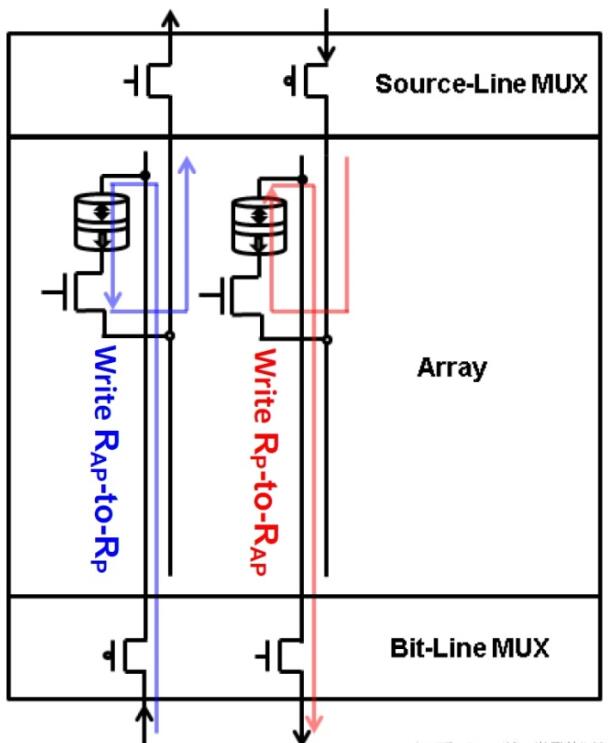

低阻态Rp和高阻态Rap的MRAM写入操作需要如图2所示的双向写入操作。要将Rap状态写到Rp需要将BL偏置到VPP,WL到VREG_W0,SL到0以写入0状态。要写入1状态,将Rap变成Rp需要反方向的电流,其中BL为0,SL为VPP,WL为VREG_W1。

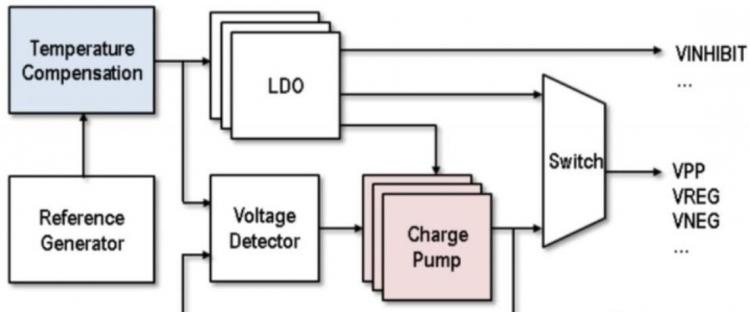

为了在260°C的IR回流焊中达到90秒的保留数据时长,需要具有高能垒Eb的MTJ。这就需要将MTJ开关电流增加到可靠写入所需的数百mA。写入电压经过温度补偿,电荷泵为选定的单元产生一个正电压,为未选定的字线产生一个负电压,以抑制高温下的位线漏电。写电压系统如图3所示。

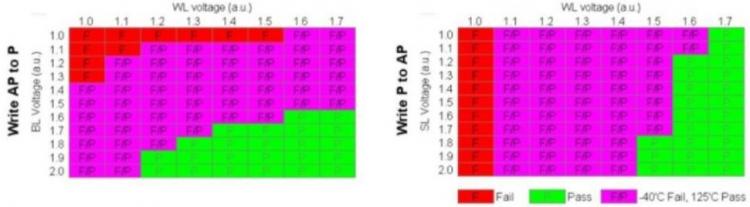

在较宽的温度范围内工作时,需要对写入电压进行温度补偿。图4显示了从-40度到125度的写入电压shmoo图,其中F/P表示在-40度时失败,而在125度时通过。

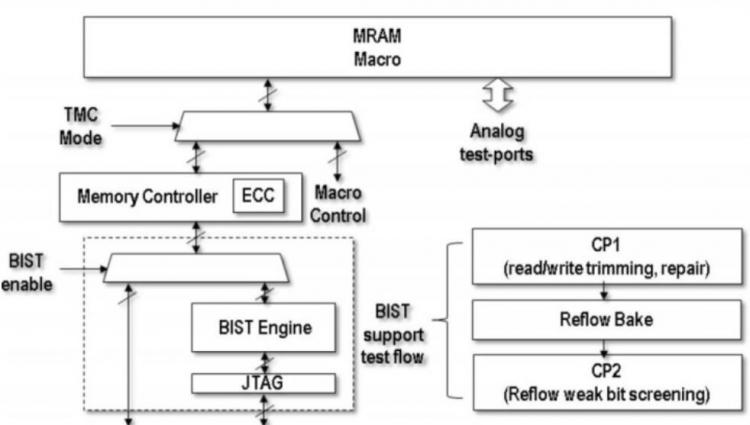

具有标准JTAG接口的BIST模块可实现自修复和自调节,以简化测试流程。实现图5中所示的双纠错ECC(DECECC)的存储控制器TMC。

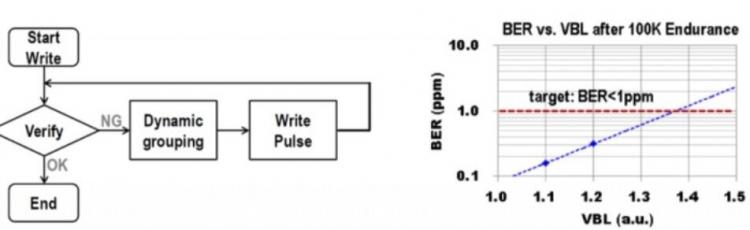

TMC实施了智能写操作算法,该算法实现了偏置设置和验证/重试时间,以实现较高的写入耐久性(>1M循环)。它包含写前读(用于确定需要写哪些位)和动态分组写入(用于提高写吞吐量),带写校验的多脉冲写入操作以及优化写电压以实现高耐久性。该算法如图6所示。

MRAM数据可靠性

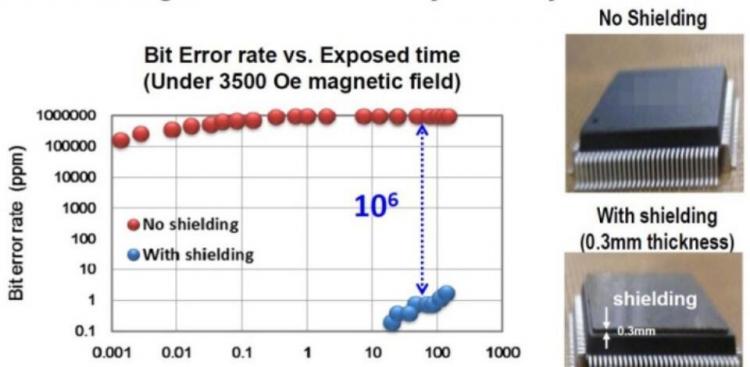

在基于自旋的STT-MRAM的许多应用中,磁场干扰是一个潜在的问题。该解决方案是在封装上沉积0.3mm厚的磁屏蔽层,如图6所示,实验表明在移动设备的商用无线充电器的磁场强度为3500Oe的情况下,暴露100小时的误码率可以从>1E6ppm降低到〜1ppm。另外在650Oe的磁场下,在125°C下的数据保存时间超过10年。

以上是 非易失性MRAM完成端口 的全部内容, 来源链接: utcz.com/a/59611.html