为省电模式FPGA平台选择合适的存储容量

从纯技术角度考虑两个最广泛使用的DRAM选项-同步DRAM(SDRAM)和减少延迟的DRAM(RLDRAM)。SDRAM tRC在过去10年中没有实质性的发展,约为48ns,这与21MT/s的RTR相关。其他基于DRAM芯片的存储设备已被设计为以密度为代价提高tRC。例如RLD RAM3的RC为8ns,与125MT/s的RTR相关。从本质上讲DRAM芯片是针对涉及确定性计算算法的顺序访问进行优化的,但高频交易却无法做到这一点。

更好的替代方法是同步SRAM存储器。尽管基于DRAM芯片的内存提供更高的内存容量,但它们无法满足交易平台缓存所要求的延迟和性能。数十年来,SRAM存储器一直是大多数高性能应用程序的首选存储器。与一般的基于DRAM芯片的解决方案相比,基于SRAM的解决方案速度提高了24倍。

在SRAM存储器中,QDR SRAM系列可提供世界上任何形式的存储器中最高的性能。QDR SRAM专门为突发随机访问而构建。借助专用于读写的端口,QDR存储器非常适合平衡的读写操作(如订单簿管理)。赛普拉斯的QDR-IV等最新的QDR SRAM更进一步,并提供了两个双向端口。当读取和写入的混合不平衡时,这使QDR-IV高效,例如TCP/IP处理查找和提要处理之类的操作就是这种情况。

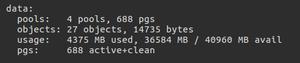

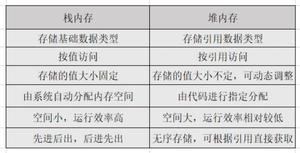

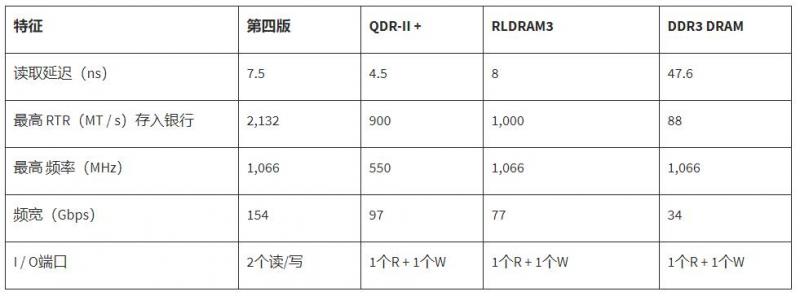

下表提供了各种核心内存技术解决方案的比较:

QDR-IV内存的RTR为2132MT/s,延迟为7.5ns。考虑到FPGA解决方案的随机存取性能至关重要,这些存储器可帮助大幅降低总体交易延迟。该SRAM的高工作频率和双端口操作可实现为要求苛刻的网络环境而构建的超低延迟数据包缓冲区。QDR-IV的无与伦比的随机事务处理率还为需要立即查询大型表或其他数据结构的自定义应用程序提供了便利。虽然DRAM是用于存储大量信息以进行数据记录的更好的存储器,但高性能SRAM可以与其结合使用,以存储计算查找或缓存用于延迟关键路径的数据。

除了RTR和延迟优势之外,许多SRAM存储芯片还集成了许多新功能,例如用于提高可靠性的纠错码(ECC),管芯端接(ODT)和去偏斜训练,以改善信号完整性。

鉴于可以产生几纳秒的竞争优势,因此在构建基于FPGA的定制解决方案时,使用的存储器类型也是至关重要的方面。由于基于QDR的存储器的固有优势,许多FPGA供应商正在将QDR存储器解决方案纳入其最新一代的高性能基于FPGA的交易解决方案中。与使用传统存储器解决方案的交易者相比,这使使用这些FPGA的交易者具有先发优势。QDR存储器得到Altera和Xilinx等领先的FPGA供应商的支持。

以上是 为省电模式FPGA平台选择合适的存储容量 的全部内容, 来源链接: utcz.com/a/50473.html